Nhìn về phía trước: Rất ít thiết bị điện tử được sử dụng trên Trái đất có thể tồn tại khi rời khỏi bầu không khí thoải mái của hành tinh. Đặc biệt, bộ xử lý phải được thiết kế để chịu được các điều kiện khắc nghiệt của không gian bên ngoài, bao gồm cả bức xạ và nhiệt độ gần như bằng 0 tuyệt đối. Có vẻ như RISC-V có thể giúp giải quyết thách thức này.

Các nhà nghiên cứu tại trường đại học công lập Thụy Sĩ ETH Zurich đã phát triển Trikarenos, một bộ vi điều khiển dựa trên RISC-V được thiết kế để hoạt động đáng tin cậy trong môi trường khắc nghiệt như không gian. Trikarenos có thể chịu được các sự kiện xáo trộn đơn lẻ (SEU) do bức xạ gây ra, đó là những thay đổi về trạng thái của một thiết bị vi điện tử do một hạt ion hóa đơn lẻ gây ra. Ngoài ra, nó có thể mang lại mức hiệu suất tương đương với “chip không gian” truyền thống trong khi chỉ tiêu thụ một phần nhỏ so với cùng mức năng lượng.

Các biện pháp đối phó phổ biến đối với điều kiện không gian thường dựa vào các công nghệ độc quyền, tăng cường bức xạ, các nút sản xuất mật độ thấp và nhân rộng rộng rãi, như giải thích bởi các nhà nghiên cứu. Những yếu tố này góp phần làm tăng chi phí và mức độ thực hiện và hiệu quả thấp. Trikarenos đặt mục tiêu giải quyết những thách thức này bằng kiến trúc CPU RISC-V 32-bit và công nghệ sản xuất 28nm “tiên tiến” do TSMC cung cấp.

Theo các nhà nghiên cứu, nút 28nm đã chứng tỏ khả năng phục hồi trước “tác động gây hại” của các sự kiện SEU do bức xạ gây ra và nó mang lại mức hiệu quả chưa từng có so với các thiết kế trước đó. Trikarenos tận dụng năng lượng cực thấp PULPissimo kiến trúc vi điều khiển, là nguồn mở, giống như kiến trúc CPU RISC-V.

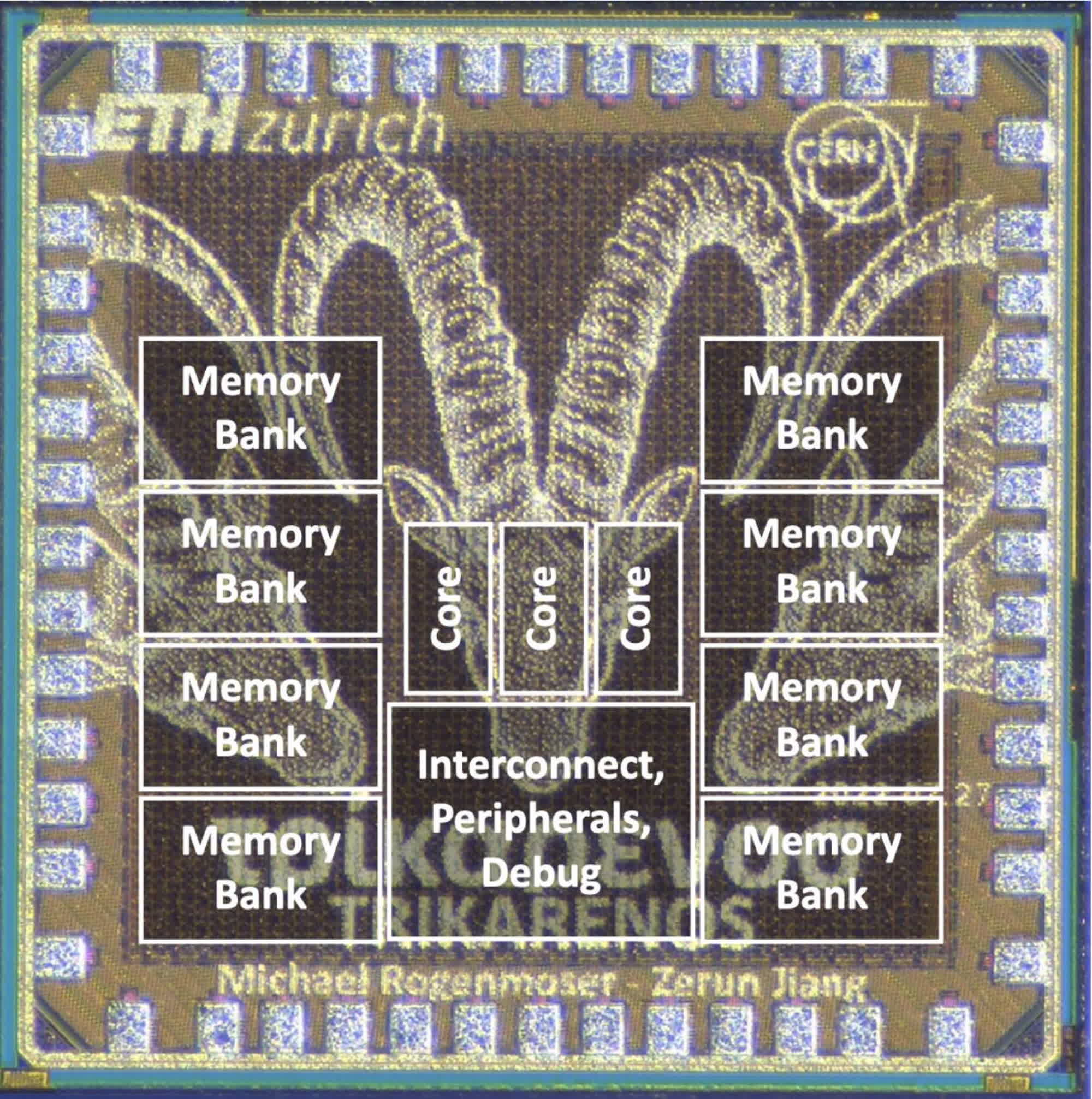

Con chip này kết hợp ba lõi điện toán Ibex dựa trên RISC-V, mỗi lõi có tốc độ lên tới 270 MHz và chúng được cung cấp dữ liệu bởi tám ngân hàng SRAM, mỗi lõi có 256 KB bộ nhớ. Ba lõi này hoạt động theo cấu hình “ba lõi khóa”, trong đó mỗi lõi thực hiện cùng một hoạt động cùng một lúc. Trong trường hợp sự kiện SEU làm hỏng một trong các lõi, một cuộc bỏ phiếu tương tự như cuộc bỏ phiếu được mô tả trong Báo cáo thiểu số sẽ xác định kết quả hoạt động chính xác.

Các thành phần kiến trúc khác được thiết kế để nâng cao khả năng chịu bức xạ bao gồm dự phòng tích hợp, ngân hàng bộ nhớ sửa lỗi và “bộ lọc bộ nhớ” liên tục đọc từng địa chỉ bộ nhớ để sửa mọi lỗi có thể sửa được. Ngoài ra, ba lõi Ibex được ngăn cách về mặt vật lý bằng khoảng cách 20 micromet xung quanh mỗi lõi.

Thiết kế ba lõi giúp tăng khả năng chịu lỗi nhưng có thể ảnh hưởng đến hiệu suất tiềm năng của bộ điều khiển. Tuy nhiên, thiết kế này dường như có khả năng mang lại mức hiệu suất tương đương với chip RAD750 dựa trên PowerPC, đã được sử dụng trong hai thập kỷ và vẫn được các cơ quan không gian lớn sử dụng cho các nhiệm vụ phức tạp nhất của họ, chẳng hạn như Kính viễn vọng Không gian James Webb. Trong những năm tới, NASA dự định thay thế RAD750 bằng CPU RISC-V hiệu suất cao do SiFive thiết kế.

So với RAD750, tiêu thụ 5 watt điện, Trikarenos có thể đạt được kết quả tính toán tương tự chỉ với 15,7 miliwatt, tạo thuận lợi cho các nhiệm vụ hạn chế năng lượng như phóng vệ tinh CubeSat. Nếu độ tin cậy cực cao không phải là yêu cầu thì ba lõi có thể hoạt động song song, mang lại hiệu suất 300% so với thiết kế bước khóa ba lõi.